4 To 16 Decoder Using 2 To 4 Decoder Verilog Code

A decoder is a circuit which has n inputs and 2n outputs, and outputs 1 on the wire. Using a 2-4 decoder, the circuit which generates traffic light combinations is as follows. Exercise How many control inputs does a 16-1 multiplexer have? Hi friends, i need to implement a vhdl code for a 4 to 16 decoder using 2 to 4 decoder in xilinx.plz can any one help me with the details relating. Design of Binary to Excess3 Code Converter using w. Design of 2: 4 Decoder using With-Select Concurre. Design of 4: 2 Encoder using with-select Concurre. Design of 1: 4 Demultiplexer using with-select Co. Design of 4: 1 Multiplexer using With-Select Conc.

4 To 16 Decoder Using 2 To 4 Decoder Verilog Code Examples

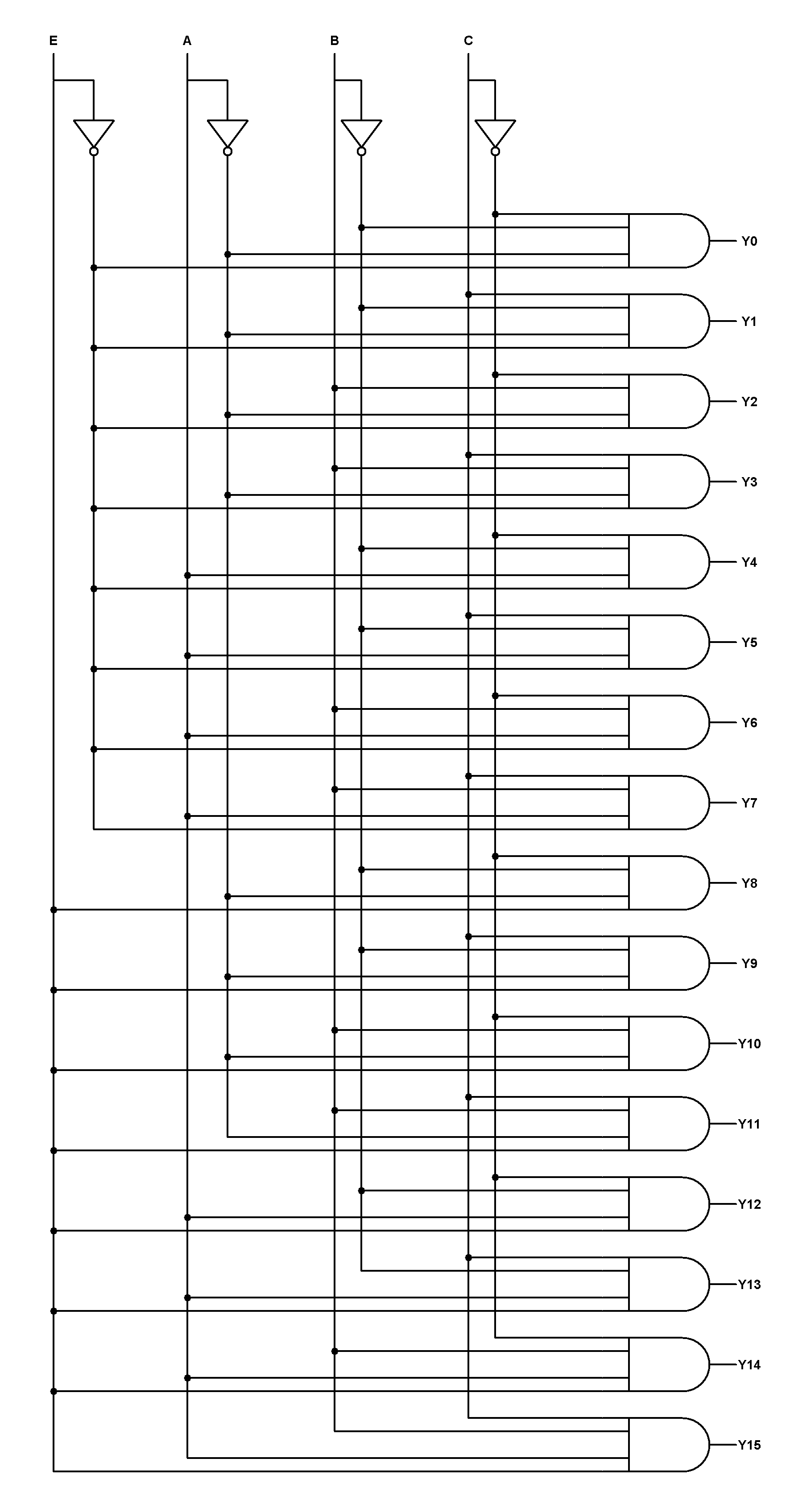

A decoder is a multiple input, multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different. The enable inputs must be ON for the decoder to function, otherwise its outputs assumes a ‘disabled’ output code word. Decoding is necessary in applications such as data multiplexing, seven segment display and memory address decoding.library ieee;use ieee.stdlogic1164.all;use ieee.stdlogicarith.all;use ieee.stdlogicunsigned.all;module decoder(a, y);input 1:0 a;output 3:0 y;reg 3:0 y;always @ (a)case(a)2’b00: y.

Decoders are combinational circuits used for breaking down any combination of inputs to a set of output bits that are all set to '0' apart from one output bit. Therefore when one input changes, two output bits will change.Lets say we have N input bits to a decoder, the number of output bits will be equal to 2^N.In this blog post, we implement a 3:8 decoder using behavioral modelling. We use case statements for this purpose. The number of input bits are 3 and number of output bits are 8.3:8 Decoder://declare the Verilog module - The inputs and output port names.module decoder3to8 (Datain,Dataout);//what are the input ports and their sizes.input 2: 0 Datain;//what are the output ports and their sizes.output 7: 0 Dataout;//Internal variablesreg 7: 0 Dataout;//Whenever there is a change in the Datain, execute the always block.always @ ( Datain )case ( Datain ) //case statement.